Komputer pipeline konsep akan kita jelaskan sebagai berikut. Throughput, didefinisikan sebagai jumlah pemrosesan yang dapat dikerjakan dalam suatu interval tertentu. Salah satu teknik yang mendorong peningkatan suatu sistem throughput yang cukup hebat disebut sebagai pemrosesan pipeline.

Pemrosesan pipeline dalam suatu komputer diperoleh dengan membagi suatu fungsi yang akan dijalankan menjadi beberapa subfungsi yang lebih kecil dan merancang perangkat keras yang terpisah, disebut sebagai tingkatan (stage), untuk setiap subfungsi. Stage-stage ini kemudian dihubungkan bersama-sama dan membentuk sebuah pipeline tunggal (atau pipe) untuk menjalankan fungsi asli tersebut.

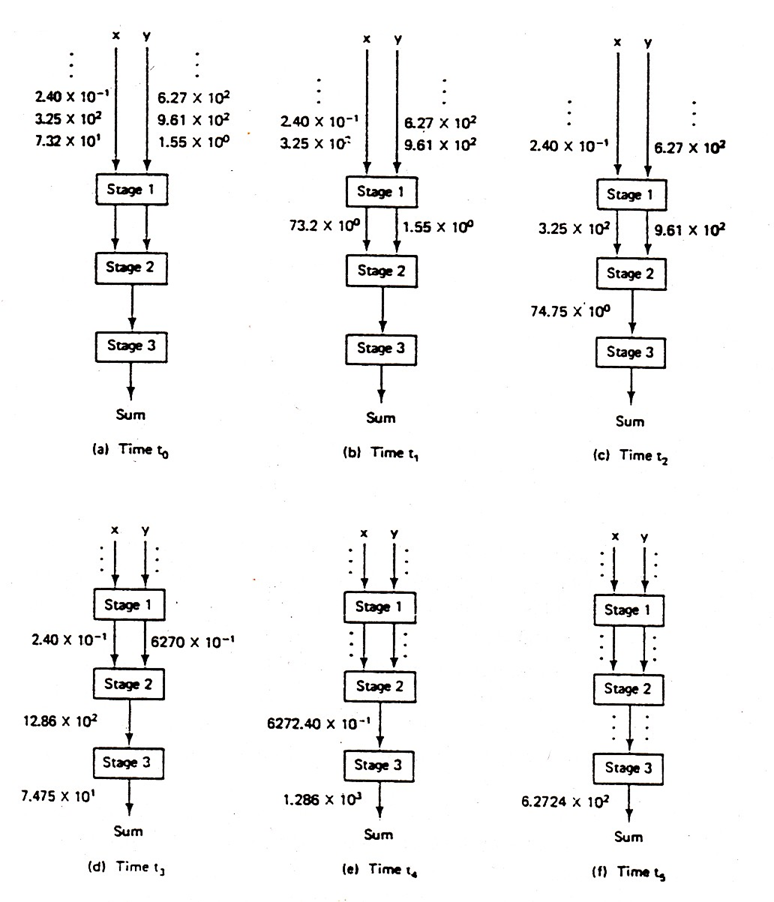

contoh:

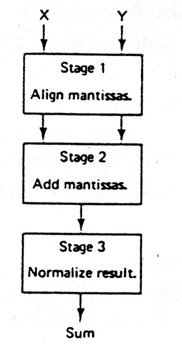

Perhatikan fungsi penambahan dua angka floating-point. Fungsi tersebut dapat kita bagi menjadi tiga subfungsi terpisah berikut ini:

- Sejajarkan mantisa-mantisa yang ada

- Tambahkan mantisa-mantisa tersebut

- Normalisasikan hasilnya

Jika kita merancang sebuah stage perangkat keras untuk setiap subfungsi ini, kita dapat menyusun fungsi tersebut sebagai pipeline tiga stage seperti diperlihatkan pada gambar.

SINKRONISASI PADA KOMPUTER PIPELINE

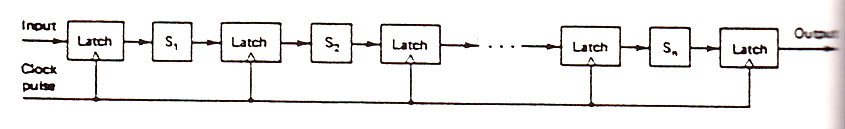

Pada semua baris perakitan industry, efisiensi suatu pipeline dapat berkurang jauh akibat bottleneck. Suatu bottleneck terjadi sewaktu pemrosesan pada suatu stasiun, atau stage, menghabiskan waktu lebih lama daripada stage lainnya. Karena itu, idealnya, kita menginginkan agar setiap stage dalam suatu pipe menghabiskan jumlah waktu proses yang sama. Meskipun kita dapat memisahkan suatu fungsi menjadi beberapa subfungsi dengan waktu proses yang relative sama, perbedaan logika dari setiap stage akan menyukarkan kita untuk menghasilkan waktu proses yang sama pada setiap stage. Untuk menyamakan waktu yang diperlukan pada setiap stage maka stage-stage tersebut harus disinkronisasikan. Hal ini biasa dilakukan dengan menyisipkan kunci-kunci (latch) sederhana(register cepat), antara stage-stage tersebut. Gambar 4 memperlihatkan sebuah pipeline linier dasar dimana setiap stage benar-benar sirkuit kombinasional yang terpisah dari stage berikutnya dari pipeline oleh adanya latch. Ada juga latch, masing-masing pada bagian pipe paling awal dan satu lagi pada bagian akhir untuk memaksa input yang sinkron dan memastikan output yang sinkron.

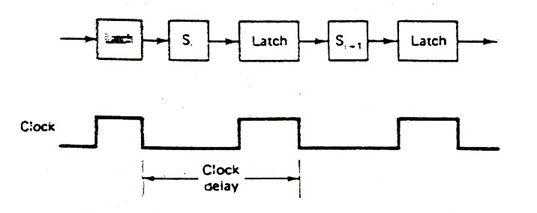

Waktu yang diperlukan untuk lewat dari suatu latch melalui stage ke latch berikutnya disebut sebagai penangguhan clock (clock delay) dan diperlihatkan pada gambar 5. Karena hanya ada satu keseragaman penangguhan clock untuk seluruh pipeline maka latch disinkronkan sesuai dengan waktu proses maksimum pada masing-masing stage individual dalam pipeline tersebut. Bahkan jika hanya ada satu stage tersebut yang mempunyai waktu proses terpanjang maka penangguhan clock di-set sebesar waktu proses yang paling lama. Dengan demikian suatu prinsip perancangan yang berhubungan dengan efisiensi adalah dengan membagi fungsi yang sedang di-pipeline menjadi beberapa subfungsi yang memiliki implementasi perangkat keras dengan waktu proses yang relative sama.

EFISIENSI KOMPUTER PIPELINE

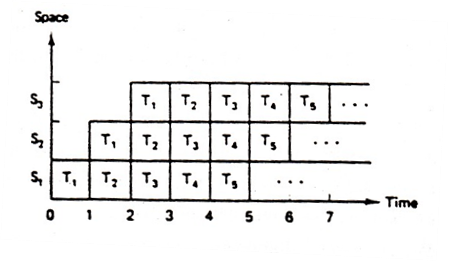

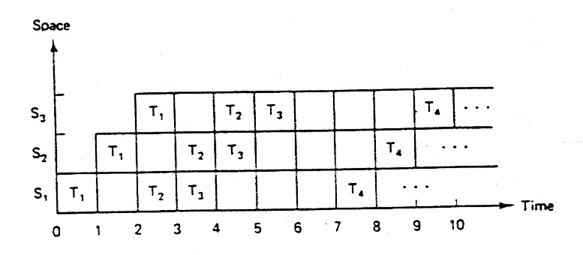

Untuk mengilustrasikan operasi-operasi yang saling tumpang tindih dalam pipeline linier digunakan suatu diagram ruang dan waktu (space-time diagram). Gambar 6 memperlihatkan diagram semacam itu untuk sebuah pipeline tiga-stage. Tiap stage diwakili oleh sumbu ruang. Tugas-tugas yang diperlihatkan dalam diagram itu berhubungan dengan sekelompok input yang bergerak sepanjang pipeline. Diagram tersebut menunjukkan kelompok input mana, atau tugas, pada stage yang mana dalam pipe tersebut dan pada penangguhan clock yang mana. Dalam gambar tersebut, inputnya terus berlanjut, dimana hal tersebut sangan efisien tetapi tidak selalu terjadi demikian. Terkadang kelompok input yang baru tidak langsung tersedia atau, seperti yang akan kita lihat nanti, terlambat. Dalam hal ini, kita mungkin akan mempunyai diagram ruang-waktu seperti pada gambar 7. Disini kelompok input kedua, T2, menunggu satu penangguhan clock lebih lama sebelum masuk ke dalam pipe; input T3 segera menyusul setelah input T2; daninput T4 menunggu tiga penangguhan clock tambahan sebelum masuk ke dalam pipe.

Dengan melihat pada diagram ruang dan waktu sebuah pipeline, kita dapat menentukan throughput pipeline tersebut, yang merupakan jumlah hasil yang dapat diselesaikan per satuan waktu. Tingkat kecepatan ini merefleksikan kecepatan hitung pipeline tersebut. Untuk menghitung throughput itu, pada umumnya kita mengabaikan waktu startup awal (initial starup time) yang diperlukan untuk mengisi pipe, yaitu waktu yang diperlukan agar kelompok input pertama memenuhi seluruh pipe tersebut. Sebagai contoh, mari kita perhatikan pipeline yang ditunjukkan pada gambir 6. Waktu startup awal pipeline ini adalah tiga penangguhan clock. Pada penangguhan clock yang kedelapan, hasil kelima sudah tersedia. Karena itu throughput-nya adalah 5/(8-3), yaitu sama dengan 1. Hal ini berarti bahwa setelah pengisian pipeline, akan tersedia satu hasil pada setiap penangguhan clock. Demikian pula throughput yang diperlihatkan pada gambar 7 adalah 4/(11-3)=0,5. Ini berarti rata-rata 0,5 hasil akan tersedia pada setiap penangguhan clock, atau satu hasil setiap dua penangguhan clock. Jadi secara umum, semakin tinggi throughput-nya semakin tinggi pula efisiensi pipeline tersebut.

Harga sebuah pipeline dapat disebabkan oleh faktor-faktor berikut ini:

- Tambahan kunci (latch) perangkat keras yang diperlukan.

- Kendali yang diperlukan untuk penjadwalan input.

- Waktu yang dihabiskan oleh data dalam latch untuk menyesuaikan diri dengan suatu penangguhan clock yang seragam.

- Jumlah rata-rata input yang tersedia agar penggunaan pipeline menjadi efisien.

Faktor terakhir, lebih daripada yang lainnya, menentukan titik potong (cutoff point) apakah proses pipeline lebih baik atau tidak. Tidak perduli seberapa efisien suatu pipeline, jika ia akan digunakan untuk satu kelompok input pada suatu waktu, semua overhead yang diperlukan untuk mem-pipeline fungsi tersebut akan membuatnya lebih lambat dan lebih mahal dibangdingkan dengan suatu fungsi yang tidak di-pipeline-kan. Namun jika jumlah kelompok input yang akan diproses pada basis regular sangat besar maka overhead pipeline tersebut lebih terjangkau.

KLASIFIKASI PIPELINE

Pipeline dapat kita klasifikasikan menurut fungsi dan konfigurasinya. Secara fungsional, mereka dikalsifikasikan menjadi tiga kelompok yaitu: pipelining aritmatika, instruksi dan prosesor. Ramamoorthy dan Li (1977) mengajukan tiga skema untuk mengklasifikasikan pipeline menurut konfigurasi dan strategi kendalinya: unifungsi atau multifungsi; statis atau dinamis; scalar atau vector.

Klasifikasi Berdasarkan Fungsi

Pipelining aritmatika. Proses segmentasi fungsi dari ALU dari system yang muncul dalam kategori ini.

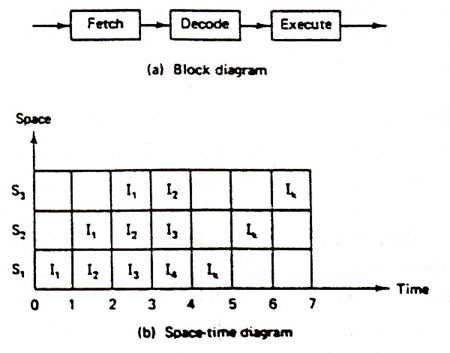

Pipelining instruksi. Dalam suatu computer nonpipeline, CPU bekerja melalui suatu siklus yang berkesinambungan dari fetch-decode-eksekusi untuk semua instrusksinya. Proses fetch suatu instrusksi tidak akan dimulai sampai eksekusi instruksi sebelumnya selesai. Untuk mem-pipeline fungsi ini, instruksi-instruksi yang berdampingan di-fetch dari memori ketika instruksi yang sebelumnya di-decode dan dijalankan. Proses pipelining instruksi, disebut juga instruction lihat-ke-muka (look ahead), mem-fetch instruksi secara berurutan. Dengan demikian, jika suatu instruksi menyebabkan percabangan keluar dari urutan itu maka pipe akan dikosongkan dari seluruh instrusksi yang telah di-fetch sebelumnya dan instruksi percabangan (branched-to instruction) tersebut di-fetch.

Contoh:

Perhatikan pipeline look-ahead tiga-stage pada Gambar 8(a). Anggap bahwa instruksi I2 merupakan cabang ke instruksi Ik. Karena itu pipeline harus dikosongkan dari semua instruksi yang telah di-fetch sebelumnya, dalam kasus ini I3 dan I4. Hal ini diperlihatkan pada diagram ruang-waktu pada Gambar 8.

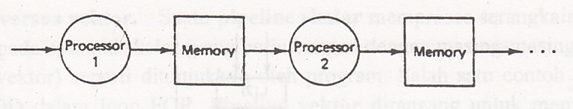

Pipelining prosesor. Sewaktu stage dari suatu pipeline merupakan procedure actual dan latch-latch saling berbagi memori antara prosesor-prosesor tersebut maka pipelining tersebut disebut pipelining prosesor.

Klasifikasi Berdasarkan Konfigurasi

Unifungsi versus multifungsi. Kemampuan suatu pipeline menjalankan satu jenis pokok operasi disebut sebagai pipeline unifungsi. Misalnya perkalian floating-point mensyaratkan pipeline agar juga menjalankan operasi yang sama setiap kelompok input. Jika pipeline dapat menjalankan fungsi-fungsi yang berbeda maka disebut sebagai pipeline multifungsi.

Statis versus Dinamis. Ketika instruksi-instruksi yang berjenis sama akan dijalankan secara bersamaan waktunya maka digunakan pipeline statis. Dengan pipeline dinamis, beberapa konfigurasi fungsional dapat muncul sekaligus.

Skalar versus Vektor. Suatu pipeline skalar memproses serangkaian operasi skalar pada operasi skalar. Pipeline vector dirancang untuk memproses instruksi vector dengan menggunakan operand vektor.

Materi Organisasi Sistem Komputer (OSK):

- Pendahuluan

- Sistem Bilangan

- Rangkaian Logika

- Organisasi Komputer Dasar

- Komputer Pipeline

My Youtube Channel: https://www.youtube.com/@ekomartantoh